数字逻辑起源于19世纪的英国数理逻辑学家Boole(布尔),后经美国克劳德.香农发展了布尔的理论,形成了数字电路分析与设计的一整套理论,这就是布尔代数,也称逻辑代数,又叫开关代数。

在数字电路中,输入与输出量之间能满足某种逻辑关系的逻辑运算电路被称为逻辑门电路。逻辑门电路是数字集成电路中最基本的逻辑单元,也是实现逻辑运算的基本单元。常用的门电路有与门、或门、非门、与非门、或非门、与或非门、异或门和同或门等。

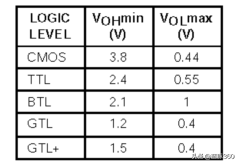

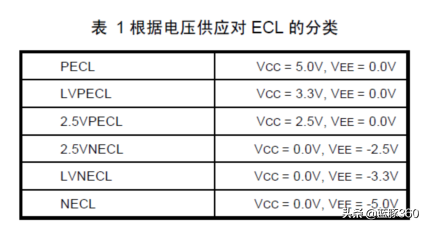

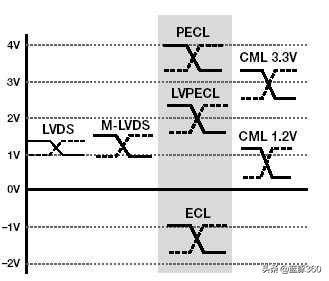

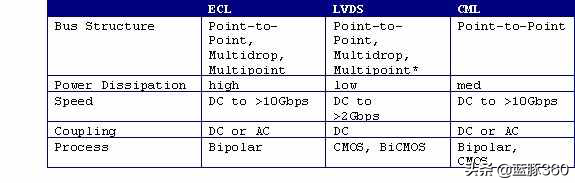

关于集成逻辑门电路,自最早的TTL(晶体管-晶体管逻辑电路)发展至当今的LVDS,经历了TTL、ECL、CMOS、CML及LVDS。其中ECL电平根据供电的不同还分为:ECL――负电源供电(一般为-5.2v)PECL――正5V供电LVPECL――正3v3供电,还有一种2.5V供电。

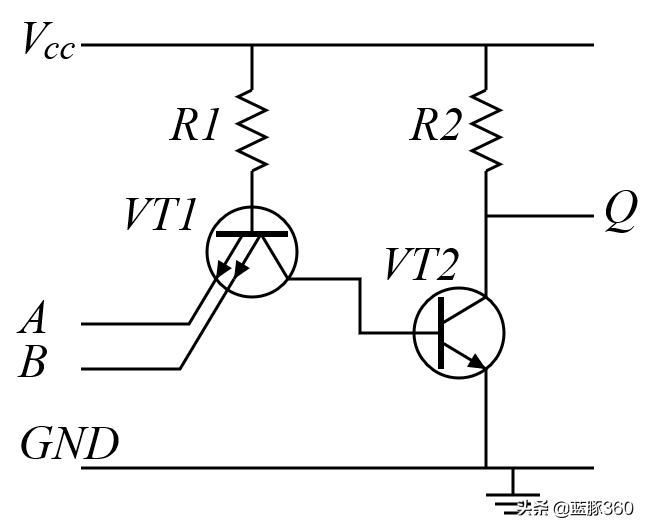

DTL(Diode-TransistorLogic):二极管-晶体管逻辑

TTL(Transistor-TransistorLogic):晶体管-晶体管逻辑

HTL(HighThresholdLogic):高阈值逻辑电路

BTL(BackplaneTransceiverLogic):

GTL(GunningTransceiverLogic):JEDEC

GTLP(GunningTransceiverLogicPlus):

ECL(EmitterCoupledLogic):射极耦合逻辑

CMOS(ComplementaryMetalOxideSemiconductor)互补金属氧化物半导体

CML(currentmodelogic):电流模式逻辑

VML(voltagemodelogic):电压模式逻辑

LVDS(LowVoltageDifferentialSignal):低电压差分信号

RTL(resistor–transistorlogic):电阻--晶体管逻辑

第一部分:TTL逻辑

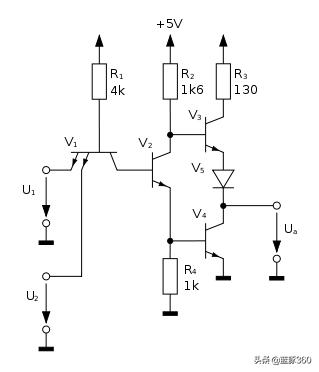

TTL是Transistor-TransistorLogic晶体管-晶体管逻的缩写,主要由BJT(BipolarJunctionTransistor即双极结型晶体管),晶体三极管和电阻构成,具有速度快的特点

TTL门电路有74(商用)和54(军用)两个系列,每个系列又有若干个子系列。54系列是工作温度范围为-55~+125℃,74系列工作温度范围为0~70℃.包括标准TTL、高速型TTL(H-TTL)、低功耗型TTL(L-TTL)、肖特基型TTL(S-TTL)、低功耗肖特基型TTL(LS-TTL)、先进低功耗型TTL和先进低功耗肖特基型TTL等三代7个系列。

TTL电平信号+5V等价于逻辑“1”,0V等价于逻辑“0”。

标准TTL--输入高电平最小2V,输出高电平最小2.4V,典型值3.4V;输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V。噪声容限是0.4V。

S-TTL(Schottky肖特基型)--输入高电平最小2V,输出高电平最小Ⅰ类2.5V(Ⅱ和Ⅲ类2.7V),典型值3.4V;输入低电平最大0.8V,输出低电平最大0.5V。

LS-TTL(LowPowerSchottky低功耗肖特基型)--输入高电平最小2V,输出高电平最小Ⅰ类2.5V(Ⅱ和Ⅲ类2.7V),典型值3.4V;输入低电平最大Ⅰ类0.7V,Ⅱ和Ⅲ类0.8V;输出低电平最大Ⅰ类0.4V,Ⅱ、Ⅲ类0.5V,典型值0.25V。

TTL电路是电流控制器件,TTL电路的速度快,传输延迟时间短(5-10纳秒),功耗大;CMOS电路是电压控制器件,CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

TTL集成电路有两种,一种为Push-Pull(又称之为totem-pole图腾柱)推挽输出,另一种为集电极开路输出。当为前者时,输出高电平最大为400uA,输出低电平最大为8mA.

TTLIC于1961年被发明,1963年成为商业化产品,此后TI发明了74和54系列TTL集成电路。1985年引入了74AS/ALSAdvancedSchottky型。

第二部分:CMOS逻辑

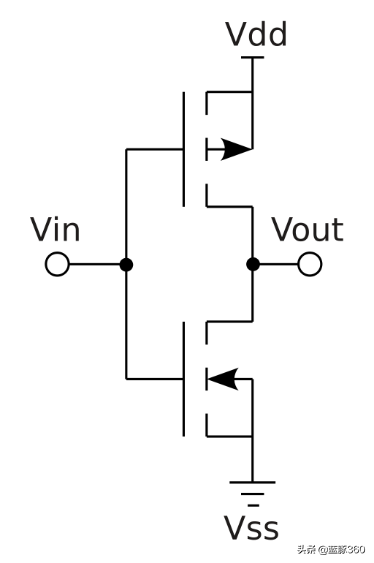

CMOS:ComplementaryMetalOxideSemiconductor互补金属氧化物半导体。电压控制的一种放大器件,是组成CMOS数字集成电路的基本单元。In1963,whileworkingforFairchildSemiconductor,FrankWanlasspatentedCMOS(USpatent3,356,858),其电路结构如下图所示,由一个N型和一个P型MOS管构成一个互补的结构。CMOS一般使用增强型场效应管enhancement-modeMOSFET。

CMOS门电路的特点就是高噪声抑制能力和低静态耗电。CMOS工作温度范围可以达到–55°Cto+125°C.。

BTLLminimaloutputcapacitance(5pFmaximum)

TTLminimaloutputcapacitance(8~15pF)

BTL端接33OHM,GTL端接50OHM。

典型的BTL输入和输出电路

典型的GTL输入和输出电路

第三部分:ECL逻辑

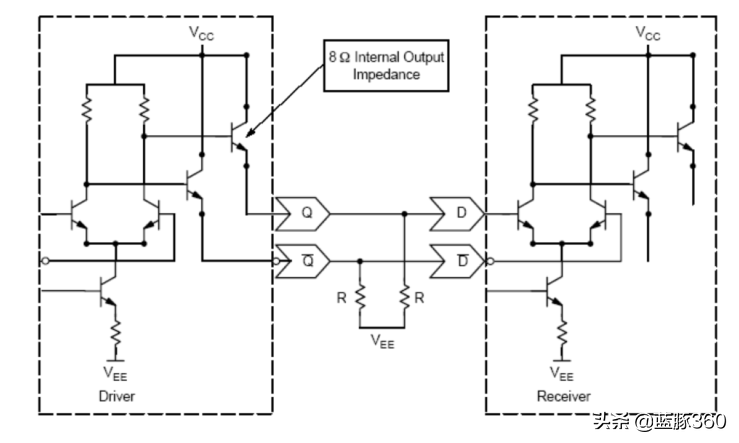

ECL(EmitterCoupledLogic),中文译名“射极耦合逻辑”,是一种适合高性能高速数字逻辑,它是一种非饱和型的双极型晶体管逻辑电路,简称ECL门,也称为电流开关逻辑(CurrentSwitchingLogic)门,它从根本上改变了饱和型电路的工作方式,在ECL电路中,三极管工作在放大和截止两种状态,由于不工作在饱和区,防止了饱和时的存储效应,使逻辑电路的开关速率大大提高,是目前各类数字集成电路中最快的一种。

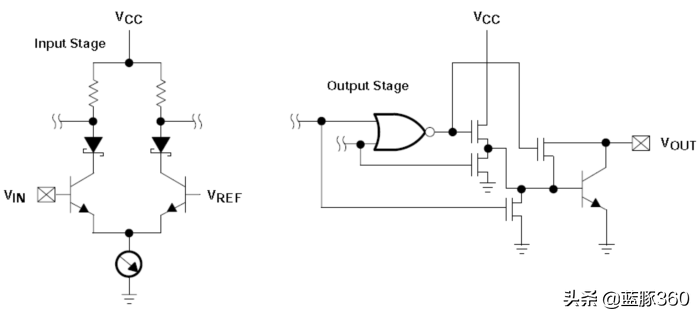

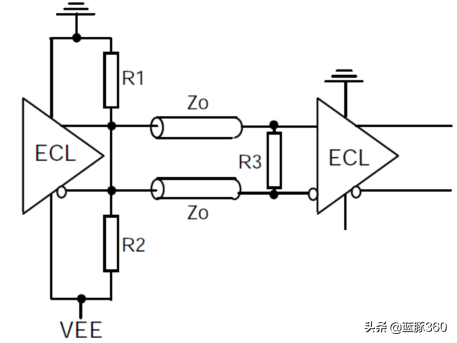

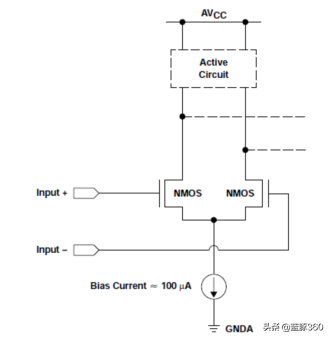

ECL在1956年由IBM公司发明,最早称为Current-steeringlogic,也称为current-modecircuit.。其工艺如下图,由一个恒流源式差放电路作为输入端接收输入信号,由差放电路的输出端接射随器形成输出。TTL的基本电路是与非门,而ECL的基本电路是或非门。

【注意】图中的下拉电阻R必不可少,它在射随器输出与一个小于输出低电平VOL的电压之间,提供一个使射随器工作于放大区的直流偏置。很多工程师在设计ECL电路时会漏掉这个电阻,导致ECL输出电路无法工作。

ECL逻辑输入和输出之间有0.8V电压摆幅,其输入阻抗高而输出阻抗低,三极管状态改变很快,而延时很低,且Fanout能力强。

ECL逻辑门电路的缺点是静态耗电较大。

ECL器件有两个供电电压VCC和VEE。当VEE接地时,VCC接正电压,这时的逻辑称为PECL(PositiveECL);当VCC接地时,VEE接负电压,这时的逻辑称为NECL(NegativeECL),一般狭义的ECL指的就是NECL。

起初的PECL器件是将VCC接+5V,后来为了直接利用广泛使用的3.3V和2.5V电压,出现了VCC=3.3V的LVPECL(LowVoltagePECL)和VCC=2.5V的2.5VPECL,有时把VCC=3.3V和2.5V的情况统称为LVPECL。NECL也有同样的情况。

需要指出的是,PECL和ECL并不是指两种不同的ECL器件,而是同一个ECL器件在不同电压供应下的表现。也就是说,一个ECL器件,当你给它的电压供应是VCC=5V,VEE=0V时,它就称为PECL,当你给它的电压供应是VCC=0V,VEE=-5V时,它就称为NECL。

相对于传统的CMOS和TTL工艺,ECL具有以下特点:

ECL低输出阻抗(6~8ohm)和高输入阻抗(可以看作无穷大)使之可以适合于驱动长的可控阻抗传输线。例如它可以驱动50~130ohm特征阻抗的传输线而交流特性并没有明显的改变。

ECL逻辑的swing小(典型800mV),高低电平之间的转换迅速,带来的交流功耗更小,而且可以减少在高速应用中串扰(crosstalk)和EMI带来的问题。

ECL器件的工艺使之能够提供差分信号,这是TTL和CMOS工艺所不具备的。而差分信号的优点众所周知——抗共模干扰能力强,接收容差大,无须额外参考电平作为判决门限。

ECL比TTL或CMOS消耗更多的直流功耗,但是ECL的交流功耗相对于频率来说近似为常数,而TTL和CMOS的交流功耗是随频率的增加而增加的。也就是说,在高速应用中,ECL器件比TTL或CMOS器件在功耗问题上并不高。

在时钟分配的应用方面,由于ECL器件对电压和温度的变化不如TTL和CMOS器件敏感,由ECL时钟驱动产生的时钟并发性更好,也就是说,输出时钟之间的skew更小。

相对于同为差分逻辑的LVDS,ECL具有以下特点:

支持更高的速度。受工艺的限制,LVDS逻辑很少有高于1.5GHz的应用,而ECL逻辑可以应用高于3GHz的场合。

支持更远距离的传输。在大背板或较长线缆的高速信号传输场景下,ECL显然比LVDS更加胜任。

对传输线阻抗的适应范围更宽。LVDS属于电流型驱动,其终端100ohm匹配电阻兼有产生电压的功能。因此,为了不改变信号摆幅,该电阻的阻值一般不能取100ohm以外的值。这意味着为了保证较好的信号完整性,LVDS传输线的阻抗只能控制在50ohm附近,而ECL可以驱动的传输线阻抗范围则宽得多。

功耗较LVDS高

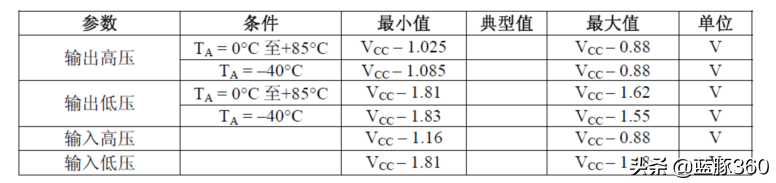

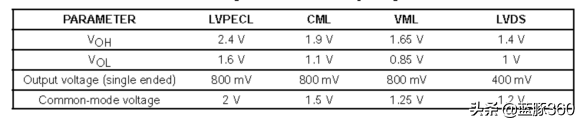

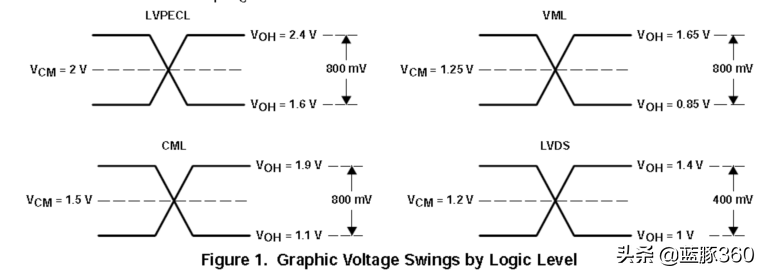

ECL逻辑的高低电平之差一般为800mV,其中心参考电平VBB根据VCC变化,一般为。因此ECL的电平随VCC的不同而不同。如:PECL,VBB=5=3.7V,VOH=4.1V,VOL=.3V;LVPECL,VBB=3.3=2V,VOH=2.4V,VOL=1.6V;对于所有的NECL(VEE=-5V、-3.3V、-2.5V),均是VBB=0=-1.3V,VOH=-0.9V,VOL=-1.7V。

国际标准定义了几类ECL逻辑,如ANSI/TIA/EIA-612"ElectricalCharacteristicsforanInterfaceatDataSignalingRatesto52Mbit/s".Thisstandar'612standardmaybeusedwiththeANSI/TIA/EIA-613standard"HighSpeedSerialInterface(HSSI)forDataterminalEquipmentandDataCircuitTerminatingEquipment"whichizedbytheTIA.

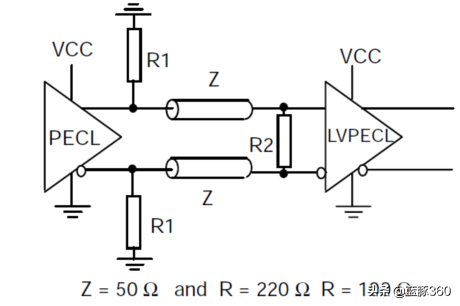

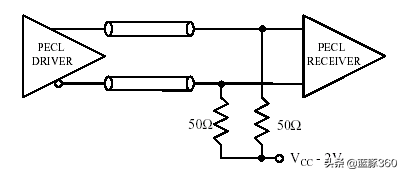

PECL逻辑

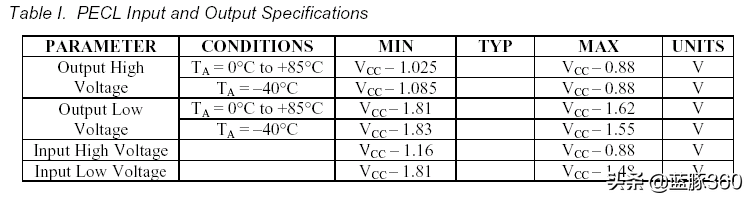

PositiveECL(也称为PseudoECL)。ECL采用-5.2V或-4.5V供电。PECL标准是从ECL标准发展而来的,二者的工作方式基本相同,区别在于PECL电路中用正电源+5V和地代替了ECL电路中的地和负电源-5.2V。所以,PECL电路较ECL电路更便于使用,而LVPECL电路则使用了正电源+3.3V和地.

当然,由于负电源供电,始终存在不便,后来随着工艺水平的提升,逐渐被PECL电平(+5V供电)所替代,后来随着主流芯片的低电源供电逐渐普及,LVPECL也就顺理成章地替代了PECL电平。

简单的说:PECL由ECL标准发展而来,但在PECL电路中使用的是正电源。PECL信号的摆幅相对ECL要小,这使得该逻辑更适合于高速数据的串行或并行连接。PECL标准最初由Motorola公司提出,经过很长一段时间才在电子工业领域推广开。

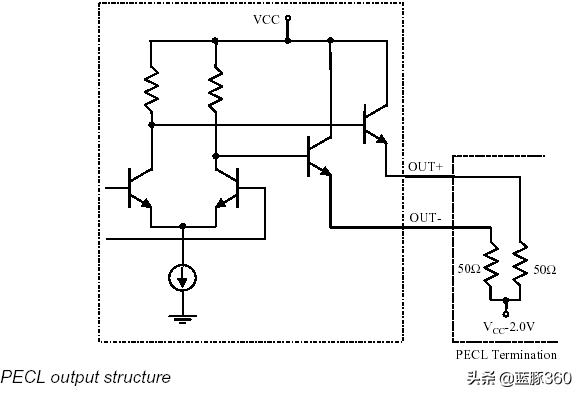

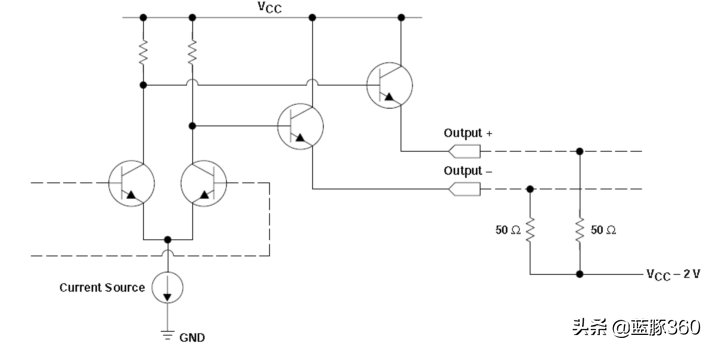

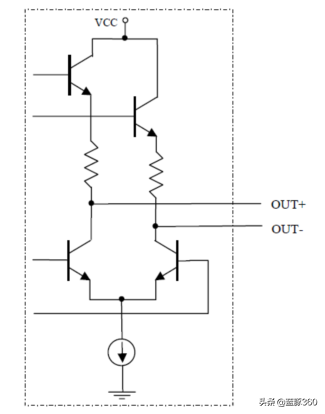

PECL逻辑的输出门结构

PECL电路的输出结构如下图所示,包含一个差分对管和一对射随器。射随器工作在正电源范围内,其直流电流始终存在,这样有利于提高开关速度,保持较快的关断时间。PECL输出的适当端接是连50Ω电阻至(VCC-2V)电平。在这种端接条件下,OUT+与OUT-的典型值为(),输出直流电流约为14mA。PECL结构的输出阻抗很低,典型值约为(4-5)Ω,这表明它有很强的驱动能力。但当负载与PECL的输出端之间有一段传输线时,低阻抗造成的背向端接失配将导致信号的高频失真。

输出门阻抗很小,一般只有4~5欧姆左右;输出的驱动能力很强;直流电流能达到14mA;同时由于输出门阻抗很小,与PCB板上的特征阻抗Z0(一般为100欧姆)相差甚远。当终端不是完全匹配的时候,信号传到终端后必然有一定的反射波,而反射波传回到源端后,也不能在源端被完全匹配,这样必然发送二次反射。正因为存在这样的二次反射,导致了PECL信号不能传输特别高的信号。一般155M、622M的信号还都在使用PECL/LVPECL信号,到了2.5G以上的信号就不用这种信号。

PECL信号的回流是依靠高电平平面(即VCC)回流的,而不是低电平平面回流。所以,为了尽可能的避免信号被干扰,要求电源平面干扰比较小。也就是说,如果电源平面干扰很大,很可能会降低PECL信号的信号质量。这就是ECL信号出现之初为何选用负电源供电的根本原因。一般情况下,我们认为GND平面是比较干净的平面。因为我们可以通过良好的接地来实现GND的平整(即干扰很小)。从这个角度来说,PECL信号和LVPECL信号都是容易受到电源(VCC)干扰的,所以必须注意保证电源平面的噪声不能太大。

对于输出门来说,P/N二个管脚不管输出是高还是低,输出的电流总和是一定的(即恒流输出)。恒流输出的特性应该说是所有的差分高速信号的共同特点(LVDS/CML电平也是如此)。这样的输出对电源的干扰很小,因为不存在电流的忽大忽小的变化,这样对电源的干扰自然就比较小。而普通的数字电路,如TTL/CMOS电路,很大的一个弊病就是干扰比较大,这个干扰大的根源之一就是对电源电流的需求忽大忽小,从而导致供电平面的凹陷。

PECL直流电流能达到14mA,而交流电流的幅度大约为8mA(800mV/100ohm),也就是说PECL的输出门无论是输出高电平还是低电平,都有直流电流流过,换一句话说PECL的输出门(三极管)始终工作在放大区,没有进入饱和区和截至区,这样门的切换速度就可以做得比较快,也就是输出的频率能达到比较高的原因之一。

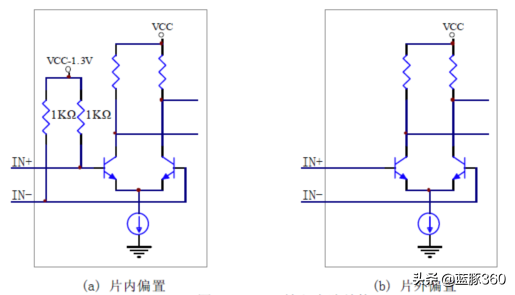

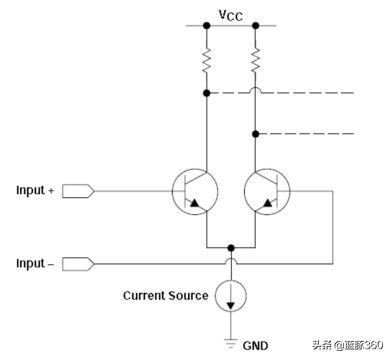

PECL逻辑的输入门结构

PECL输入结构如下图所示,它是一个具有高输入阻抗的差分对,该差分对共模输入电压需偏置到(),这样允许的输入信号电平动态范围最大。它分为有输入直流偏置和没有输入直流偏置(需要外接直流偏置的)等两种。一般情况下,ECL/PECL/LVPECL信号的匹配电阻(差分100欧姆)都是需要外加的,芯片内部不集成这个电阻。为输入门的中间电平(即输入信号的共模电压),对于LVPECL来说大约为2V,对于PECL来说为3.7V。也就是说,我们要判断一个PECL/LVPECL电平输入能否被正常接收,不仅要看交流幅度能否满足输入管脚灵敏度的要求,而且要判断直流幅度是否在正常范围之内(即在左右,不能偏得太大,否则输入门将不能正常接收)。在这一点上与LVDS有很大的差别,务必引起注意。

在+5.0V和+3.3V供电系统中,PECL接口均适用,+3.3V供电系统中的PECL常被称作低压PECL(LVPECL)。在使用PECL电路时要注意加电源去耦电路,以免受噪声的干扰,另外,PECL输出采用交流还是直流耦合对负载网络的形式将会提出不同的要求。

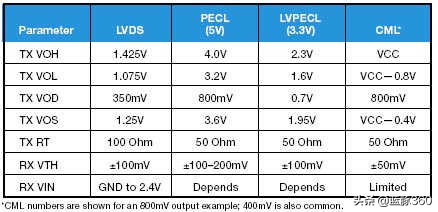

PECL电路的输出VOH的典型值为4.1V(VCC–0.9V),VOL的典型值为3.3V(VCC–1.7V)。LVPECL电路的VOH的典型值为2.4V(VCC–0.9V),VOL的典型值为1.6V(VCC–1.7V)。

LVPECL逻辑

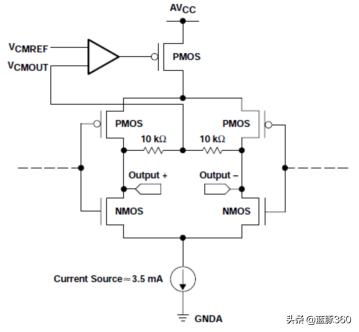

LVPECL采用低电压3.3V或2.5V供电,其接口高/低电平与标准PECL逻辑会有差异。其余同上。输入和输出段电路结构如下列两个电路图所示。

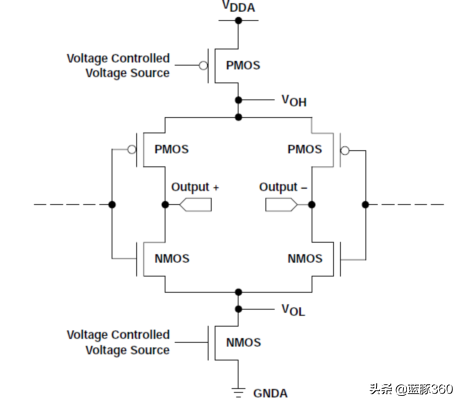

LVPECL输出段的典型电路结构

LVPECL输入段(inputstage)的典型电路结构

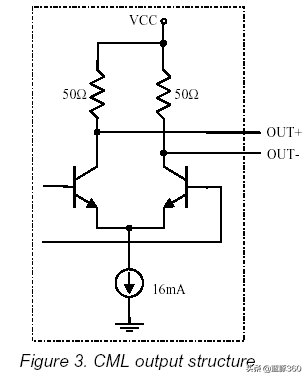

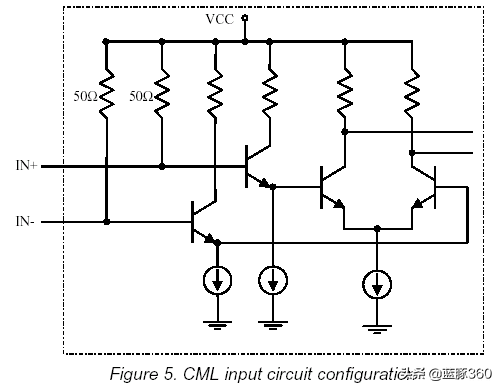

第四部分:CML逻辑

CML逻辑是一种比较简洁的逻辑电路,它内置匹配电阻(输入输出都有50欧姆的电阻),这样使用户应用时特别简单,不需要象ECL一样加一堆的偏置电阻和匹配电阻。CML的特点是:high-speedcapabilities,adjustablelogicoutputswing,leveladjustment,andadjustableslewrate.

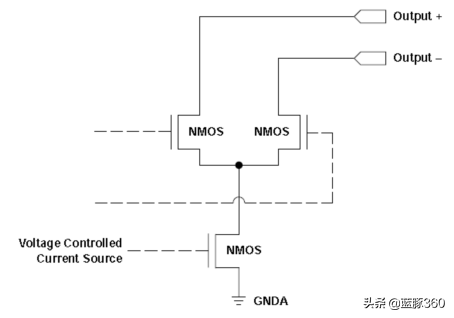

CML逻辑输出结构

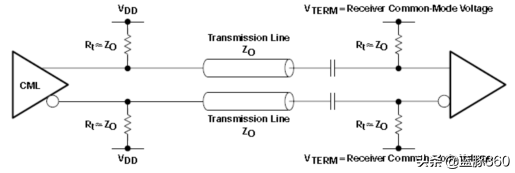

CML的输出电路形式是一个差分对管,该差分对的集电极电阻为50Ω,如图所示。

CML输出段的典型电路结构

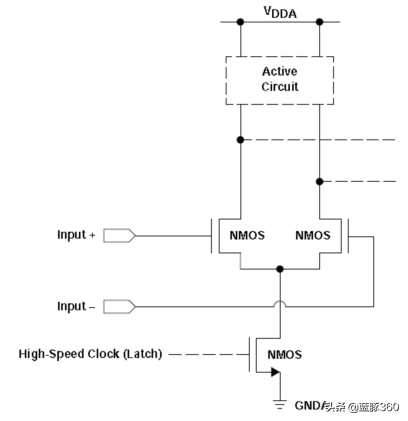

CML输入段的典型电路结构

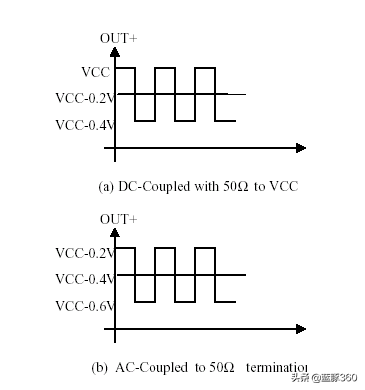

输出信号的高、低电平切换是靠共发射极差分对管的开关进行控制的。假定电流源的典型值为16mA,CML输出负载为上拉至VCC的50Ω电阻,则单端CML输出信号的摆幅为VCC至()。在这种情况下,CML差分输出信号摆幅典型值为800mV,共模电压为()。对同一个电流源来说,若CML输出采用交流耦合至50Ω负载,这时的直流阻抗由50Ω集电极电阻决定。CML输出共模电压变为(),差分信号摆幅仍为800mVP-P。交流和直流耦合情况下输出波形如图示。

A、由于输出门也有50欧姆的匹配电阻,使得二次反射信号也能被这个电阻匹配掉,这样就避免了多次反射导致的信号劣化(振铃现象)。在这一点,与ECL电平相比有很大的改进,所以CML电平所能支持的速率比较高,一般情况下,2.5G/10G这样的高速信号都是采用CML电平来传输,不再采用LVPECL信号。从光口的抖动指标来看,CML电平具有抖动指标小的特性。

对比3种电平抖动方面的性能:CML最优、ECL次之、LVDS比较差。这就是一般情况下LVDS信号很少作为光接口驱动信号的原因之一(当然,输出信号幅度比较小、电流驱动能力比较弱应该也是原因之一。)

B、同样的,CML电平也是采用恒流驱动方式;

C、CML电平的输出AC摆幅能达到800mV;

D、一般情况下,CML电平可以是直流耦合方式对接,也可以是交流耦合方式对接。

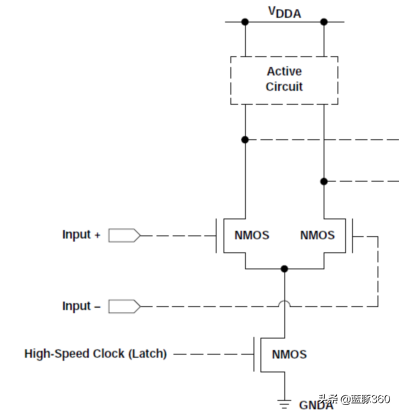

CML逻辑输入结构

CML输入结构有几个重要特点,这也使它在高速数据传输中成为常用的方式。CML输入结构的输入阻抗为50Ω,易于端接。输入晶体管作为射随器,后面驱动一个差分对放大器。下图分别为CML逻辑门电路的输入门电路结构模型。

SignalswingcomparisonsshowingdifferentialoutputvoltageanddriveroffsetsofLVDS,ECLandCML.

第五部分:VML逻辑

VML逻辑输出结构

VML逻辑输入结构(输入端IN+和IN-需要上拉电阻)

同CML逻辑一样,VML输入端需要加上拉电阻。

第六部分:LVDS逻辑

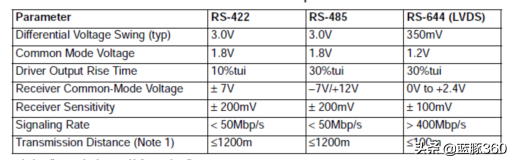

LVDS接口又称RS644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。LVDS逻辑标准见ANSITIA/EIA-644和–1996.

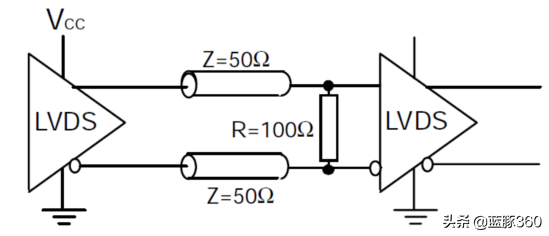

最基本的LVDS器件就是LVDS驱动器和接收器。LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5mA。LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。

LVDS技术在两个标准中被定义:ANSI/TIA/EIA644(1995年11月通过)和(1996年3月通过)。这两个标准中都着重定义了LVDS的电特性,包括:

①低摆幅(约为350mV)。低电流驱动模式意味着可实现高速传输。ANSI/TIA/EIA644建议了655Mb/s的最大速率和1.923Gb/s的无失真通道上的理论极限速率。

②低压摆幅。恒流源电流驱动,把输出电流限制到约为3.5mA左右,使跳变期间的尖峰干扰最小,因而产生的功耗非常小。这允许集成电路密度的进一步提高,即提高了PCB板的效能,减少了成本。

③具有相对较慢的边缘速率(dV/dt约为0.300V/0.3ns,即为1V/ns),同时采用差分传输形式,使其信号噪声和EMI都大为减少,同时也具有较强的抗干扰能力。

所以,LVDS具有高速、超低功耗、低噪声和低成本的优良特性。

LVDS的应用模式可以有四种形式:

①单向点对点(pointtopoint),这是典型的应用模式。

②双向点对点(pointtopoint),能通过一对双绞线实现双向的半双工通信。可以由标准的LVDS的驱动器和接收器构成;但更好的办法是采用总线LVDS驱动器,即BLVDS,这是为总线两端都接负载而设计的。

③多分支形式(multidrop),即一个驱动器连接多个接收器。当有相同的数据要传给多个负载时,可以采用这种应用形式。

④多点结构(multipoint)。此时多点总线支持多个驱动器,也可以采用BLVDS驱动器。它可以提供双向的半双工通信,但是在任一时刻,只能有一个驱动器工作。因而发送的优先权和总线的仲裁协议都需要依据不同的应用场合,选用不同的软件协议和硬件方案。

为了支持LVDS的多点应用,即多分支结构和多点结构,2001年新推出的多点低压差分信号(MLVDS)国际标准ANSI/TIA/EIA899-2001,规定了用于多分支结构和多点结构的MLVDS器件的标准。

LVDS用于低压差分信号点到点的传输,该方式有若干优势,使其更具有吸引力。较小的信号摆幅使得功耗较低,一般负载阻抗为100Ω的差分线上的电流不超过4mA。这一特征使得LVDS适合做并行数据传输。此外信号的电平很低,从而使得该结构可以在2.5V的低电压下工作。LVDS输入信号电压可以从0V到2.4V变化,单端信号摆幅为400mV,这样允许输入共模电压从0.2V到2.2V范围内变化,也就是说LVDS允许驱动器和接收器两端地电势有±1V的落差。

LVDS逻辑输出结构(NMOS)

LVDS输出段的典型电路结构

LVDS电路差分输出阻抗典型值为100Ω。

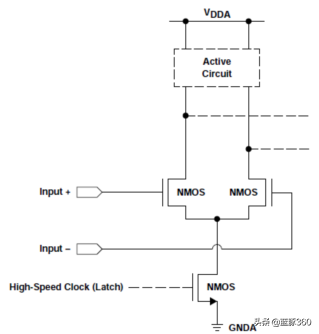

LVDS逻辑输入结构

LVDS输入结构如下图所示,IN+与IN-输入差分阻抗为100Ω。为适应共模电压宽范围内的变化,输入级还包括一个自适应电平转换电路,该电路将共模电压设置为一固定值,该电路后面是一个施密特触发器。施密特触发器的输入门限具有滞回特性,触发器后级是差分放大器。

LVDS输入段的典型电路结构

LVDS电平与PECL和CML电平来说有几个比较显著的特点:

LVDS电平的驱动电流很小才4mA,所以功耗特别小,输出摆幅为400mV。当系统种有很多这种信号的时候(如TDCS6440G芯片有64对的622M的LVDS收发),它的功耗优势就能体现出来。在我们设计系统的过程中,芯片的功耗和系统的散热一直是重点考虑的问题。

LVDS电平可以做成支持热插拔,用作背板驱动,而PECL/LVPECL和CML电平一般情况下不支持热插拔,不能用在背板驱动。从电路的结构上我们也可以看到LVDS的输出门结合了PECL电平和CML电平的特点,并且通过串阻的限流,可以限制浪涌电流的产生,避免门的损坏,CML电平也能做成支持热插拔,但是普通的CML电平不一定能支持热插拔。

LVDS的输入门与其他输入门有一个显著的特点,前面有一个类似于直流电平漂移适配电路(ADAPTIVELEVELSHIFTER),这个电路能够适应直流电平(common-modevoltage)的变化的,使得输入直流电平变化范围可以很宽(0.2V~2.2V)。也正因为这样,LVDS比其他信号有更强的共模抗干扰能力。因为LVDS差分线一般情况下离得比较近,一旦有干扰,P、N二个信号会同时受到干扰,这样导致P/N同时上升或者下降,而LVDS通过这个均衡电路就能很好地适应这种干扰,从而提高共模抗干扰能力。

这一点与PECL电平有显著的差别,PECL信号是要求直流电平在左右,偏差不能太大,否则就不能正常接收。

LVDS输入门内部集成了100欧姆的匹配电路,所以芯片外部就不需要再加匹配电阻,大大简化了设计的难度。如果在BGA下需要加一堆的匹配电阻的话,其设计难度确实不是一般的大。

LVDS还能容忍收发器之间的GND电平差达到+-1V左右。这个特性使得LVDS在用于二个不同系统之间的互连的时候就显得特别方便,它可以不要求二个系统的GND平面完全等电势。例如,主框与从框之间可以通过LVDS信号互连起来。

第七部分:逻辑电路之间的连接与耦合

PECL与PECL连接

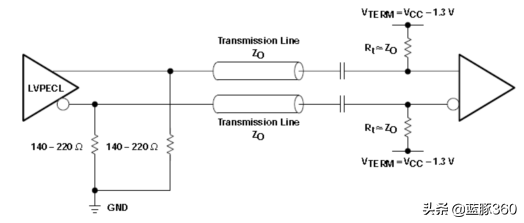

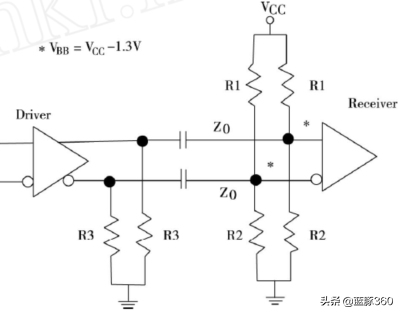

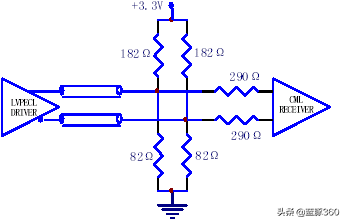

两个LVPECL逻辑门电路之间--DC直流耦合

图5.PECL直接耦合连接图示

图5的匹配方式是PECL电路的基本匹配模型,其中2个50欧姆的作用,既是交流匹配的电阻(靠近输入端放置),也充当直流回路的偏置电阻。由于是同一种电平对接,AC摆幅和DC电平没有问题(符合下表),

两个LVPECL逻辑门电路之间--交流耦合

Inthecaseofac-coupling,becausethereisnolongeradcpathforfallingedges,theLVPECLdriveroutputsshouldbegroundedviasmallresistorsintherange140Ω–220Ω,theterminationresistorsshouldbeat

VCC–1.3V,becauseifthereceiverrequiresanLVPECLsignalinglevel,thecommon-mode

voltageswing,thentheterminationresistorsRtshouldbeterminatedtothecommon-modeinputvoltageofthereceiver.

图7

图7是从图5演化而来,R1=130/R2=82(3v3);R1=82/R2=130(5v)。其中R1/R2既充当交流匹配电阻(50欧姆),也充当直流偏置电阻。缺点是:4个电阻都必须放在离输入端很近的地方,对PCB布板造成困难。匹配电阻功耗比较大,如果路数很多的话,对单板的功耗来说是一个比较大的问题(静态电阻很小)。

图8

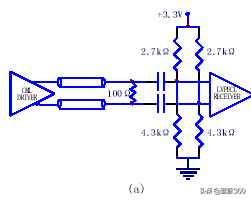

图8是一种资料上很少提,但是却很有用的电路方式,其中R1=140~200欧姆(3.3V供电时)/R1=270~330欧姆(5V供电时),R2=100欧姆。R1为输出门提供偏置电流,R2为交流信号提供匹配。输入门的直流电平直接利用输出门的直流电平,并不需要外来的上下拉电阻来提供。这种电路的优点是电阻个数很少,只有3个。只有R2一个电阻必须放在离输入门比较近的地方,R1放置的地方可以比较随便,只要不引入过长的线头(过长的线头会导致反射)就可以,PCB布板比较容易处理。这种电路的功耗比图7小得多。

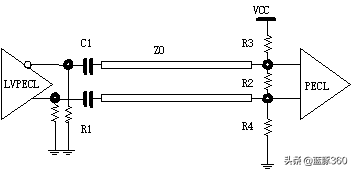

LVPECL与PECL连接

对于LVPECL和PECL来说,虽然AC的摆幅相同(800mV),但是直流电平不一样,所以无法之间用DC耦合对接起来。在这种情况下,我们可以考虑用AC耦合方式来处理。在设计PECL交流耦合电路的时候,我们需要考虑:

²给PECL输入提供VCC–1.3V的电压偏置,且输入阻抗应该和信号传输线的阻抗匹配;

²选择合适的电阻给PECL输出提供电流路径,同时要避免PECL输出过大电流。

²此外,还要注意系统的功耗和复杂度。

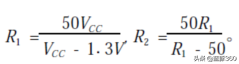

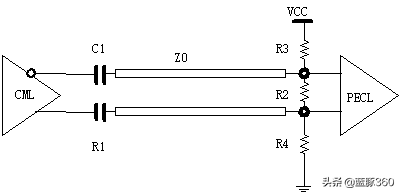

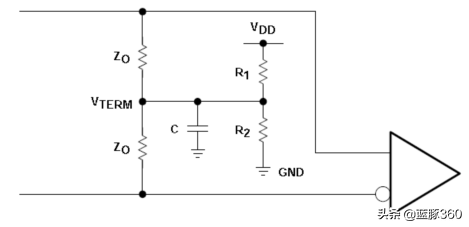

图9

其中:R1=140~200欧姆属于直流偏置电阻,C1为耦合电容,可以放在线上的任何一个地方,不一定在源端,也不一定要在末端。R2=100欧姆属于交流匹配电阻,一定要放在末端。R3、R4为K级别的电阻,必须满足R4/(R3+R4)=()/VCC的比值就可以。R3/R4为输入端提供直流电平,所以对PCB上的位置没有特殊要求,只需要不引入长线头就可以。

优点:对于交流耦合来说,器阻容器件的个数算是比较少;只对一个电阻的位置(R2)有要求,其他的没有要求;功耗也比较小。这种电路还带来另外一个优点,那就是当LVPECL输出没有交流信号的时候,那么输入端却可以依靠100欧姆(R2)的电阻使得P/N维持一个电压差,从而保证输入端的稳定(恒为“0”或者“1”)。大家可以联想到芯片LOS信号的检测机制――看输入的信号是否为长“0”或者长“1”,为芯片的正确检测LOS提供了保证。

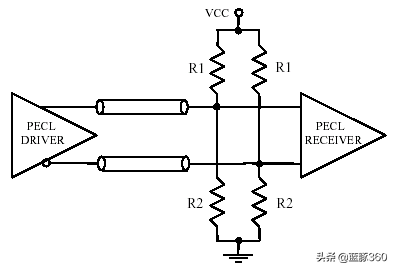

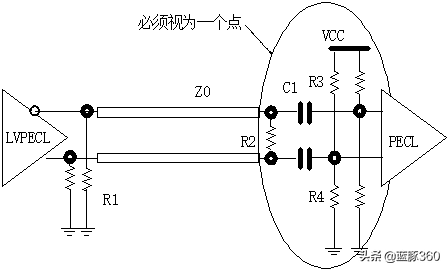

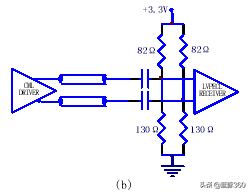

图10

图10电路是很多资料推荐使用的,从原理上分析没有错,但是从实用的角度来说并不是最佳方案。电路(a)种的R2/R3既做为交流匹配电阻,又做为输入直流电平,由于R2/R3共4个电阻必须放在输入引脚附近,所以可能导致PCB布板困难。同时功耗也比较大。如下图为类似(a)的一个实例电路。

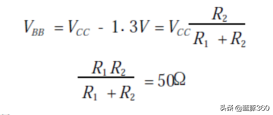

其中,由R1和R2组成的电阻分压网络给PECL输入提供了偏置电压VBB(VCC–1.3V),同时R1和R2还要和信号传输线的阻抗Z0匹配。假设Z0=50Ω,则

解方程可得

当信号为PECL电平,即VCC=5V时,R1=68Ω,R2=180Ω;当信号为LVPECL电平,即VCC=3.3V时,R1=82Ω,R2=130Ω。

PECL的输出静态电平典型值为VCC–1.3V,在选择直流偏置电阻R3时仅需该电阻能够提供14mA到地

的通路,这样R3=(VCC–1.3V)/14mA。在+3.3V供电时,R3=142Ω;+5.0V供电时,R3=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,+3.3V供电时,R3可以从142Ω到200Ω之间选取,+5.5V供电时,R3可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。

电路(b)应该说有比(a)比较大的改进,虽然从电阻的个数上来说还多一个,但是PCB布板容易,并且功耗比较小。其R2/R3阻值可以是K级别的。

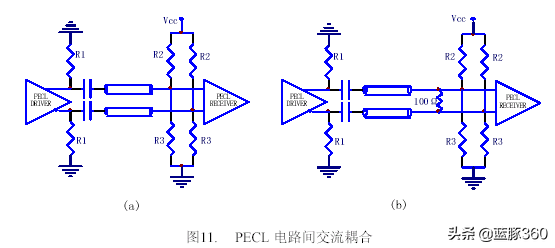

图11

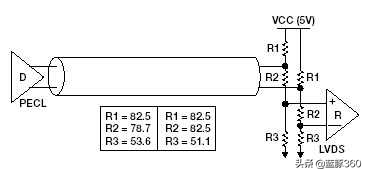

PECL与LVDS接口的连接

上面的连接电路提供一个50mV的failsafe偏置电压给LVDS接收机。

R1//(R2+R3)=50Ohms为PECL提供一个50OHM的匹配。

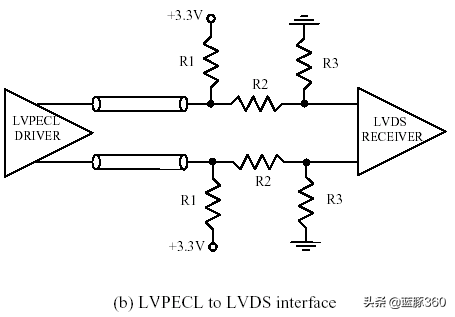

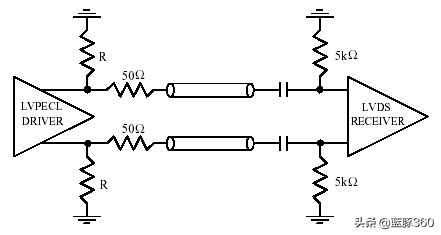

²LVPECL与LVDS接口的连接

对于LVPECL输出,LVDS输入的信号来说,LVPECL的直流输出电平为2V左右,而LVDS的直流输入可以为0.2V~2.2V,所以直流电平本身不是关键。对于交流电平来说LVPECL输出最大为800mV,甚至超过1V,而LVDS的输入交流电平一般不能承受800mV的输入(具体还得看芯片资料的说明),一般是认为最大在400mV左右。所以如何把交流幅度调整到LVDS能够接受的范围才是关键。可以考虑采用直流耦合和交流耦合,如下面两图所示。

图12

以上是LVPECL到LVDS的DC和AC二种耦合的示意图。

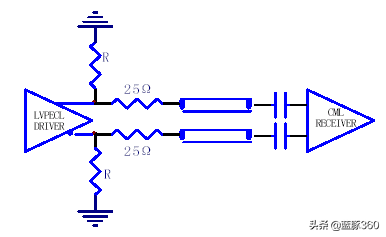

LVPECL与CML接口的连接

图13

一般情况下,二种不同直流电平的信号(即输出信号的直流电平与输入的直流电平相差比较大),我们比较提倡使用AC耦合,这样输出的直流电平与输入的直流电平独立。

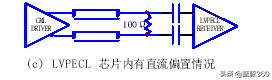

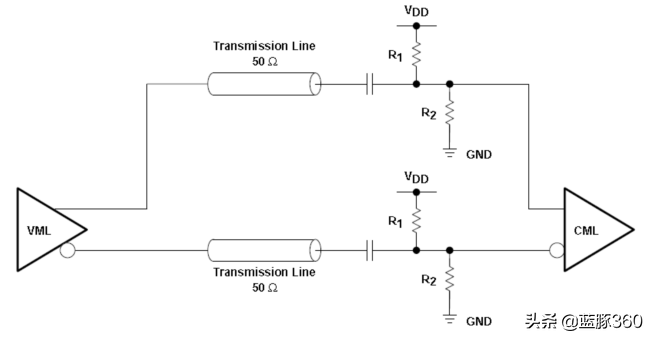

CML与LVPECL接口的连接

对于CML输出、LVPECL输入来说,由于直流电平相差很大,所以一般采用交流耦合方式。而CML输出的交流幅度一般不会大于LVPECL接收的交流幅度,所以交流方面只需要考虑匹配就可以,不需要考虑幅度。提供的匹配电路图如下:

图14

图15

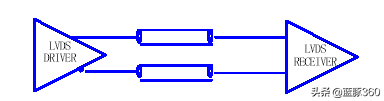

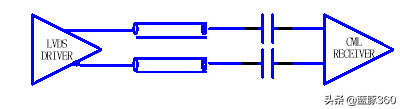

LVDS与LVDS接口的连接

应该说LVDS之间的对接是最简单的对接。可按如下图所示连接。

图16

Rt=100OHM为典型值。

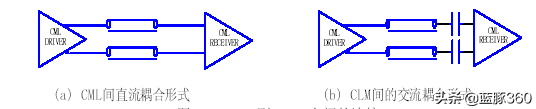

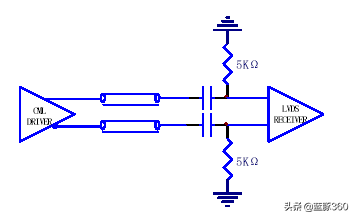

CML与CML接口的连接

图17

CML之间的连接使用直流耦合就可以,但如果二个芯片的供电电源不同就必须用交流耦合。CML输出段使用开源OpenSourceNMOSTransistors.为驱动上升沿,输出驱动需要外接上拉电阻至VDD。

CML直流耦合图示(Rt等于特性阻抗)

CML交流耦合图示

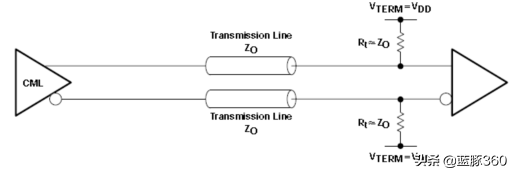

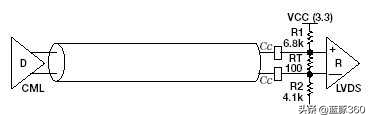

LVDS与CML接口的连接

一般情况下,不会存在LVDS与CML之间的对接,因为CML电平一般用在高速信号,如2.5G/10Gbps等场合,而LVDS一般很难用在那么高的速率(DC~2.5Gbps)。在这里要注意的是,输出交流幅度是否落在输入交流幅度之内。

图18

CML与LVDS接口的连接(Interoperation)

a30mVfailsafebiasfortheLVDSreceiver.

采用如上图所示的AC交流耦合。

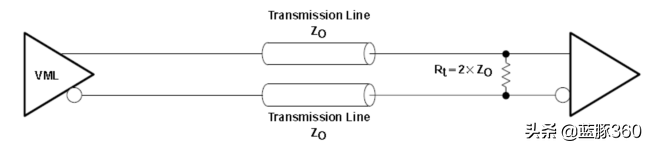

VML与VML接口的连接

VML直流耦合图示

VML无须外接上拉或下拉电阻。

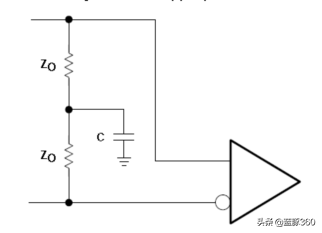

有时为消除差分differential-skew和共模噪声common-modenoise.,可使用下面的端接电路。

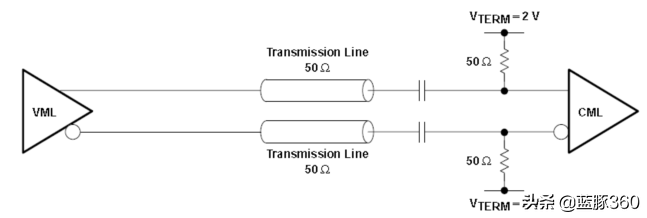

VML交流耦合图示

VML与CML的连接

R1//R2=Z0=50OHM

-

实探开市客华南首店:开业次日进场仍需排队半小时

2025-12-26 -

MECA挑战赛再创佳绩 U17联盟摘得两冠两亚

2025-11-26 -

余承东再喊遥遥领先!问界新M7来了:满油满电能跑1300km

2025-04-18 -

古筝乐理知识

2025-07-31